source

GOWIN built-in JTAG Logic Analyzer

The GOWIN FPGA have a built-in Logic Analyzer, which is made of extra RTL added to the project, generated from the IDE.

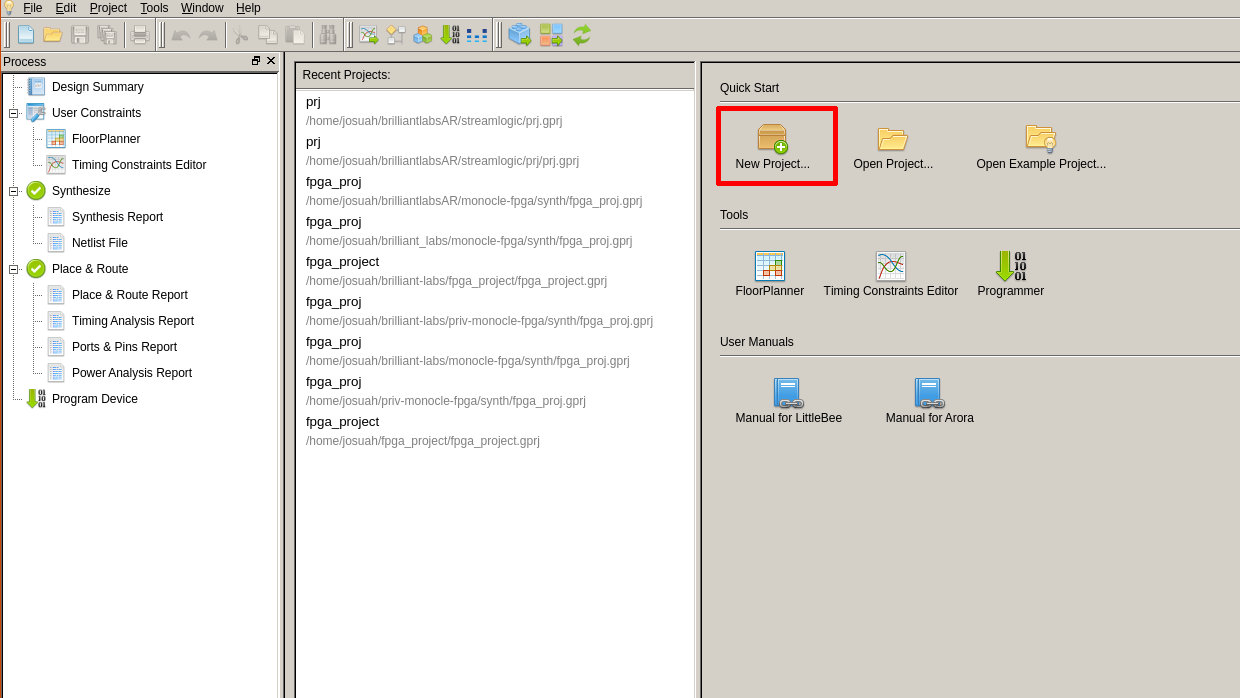

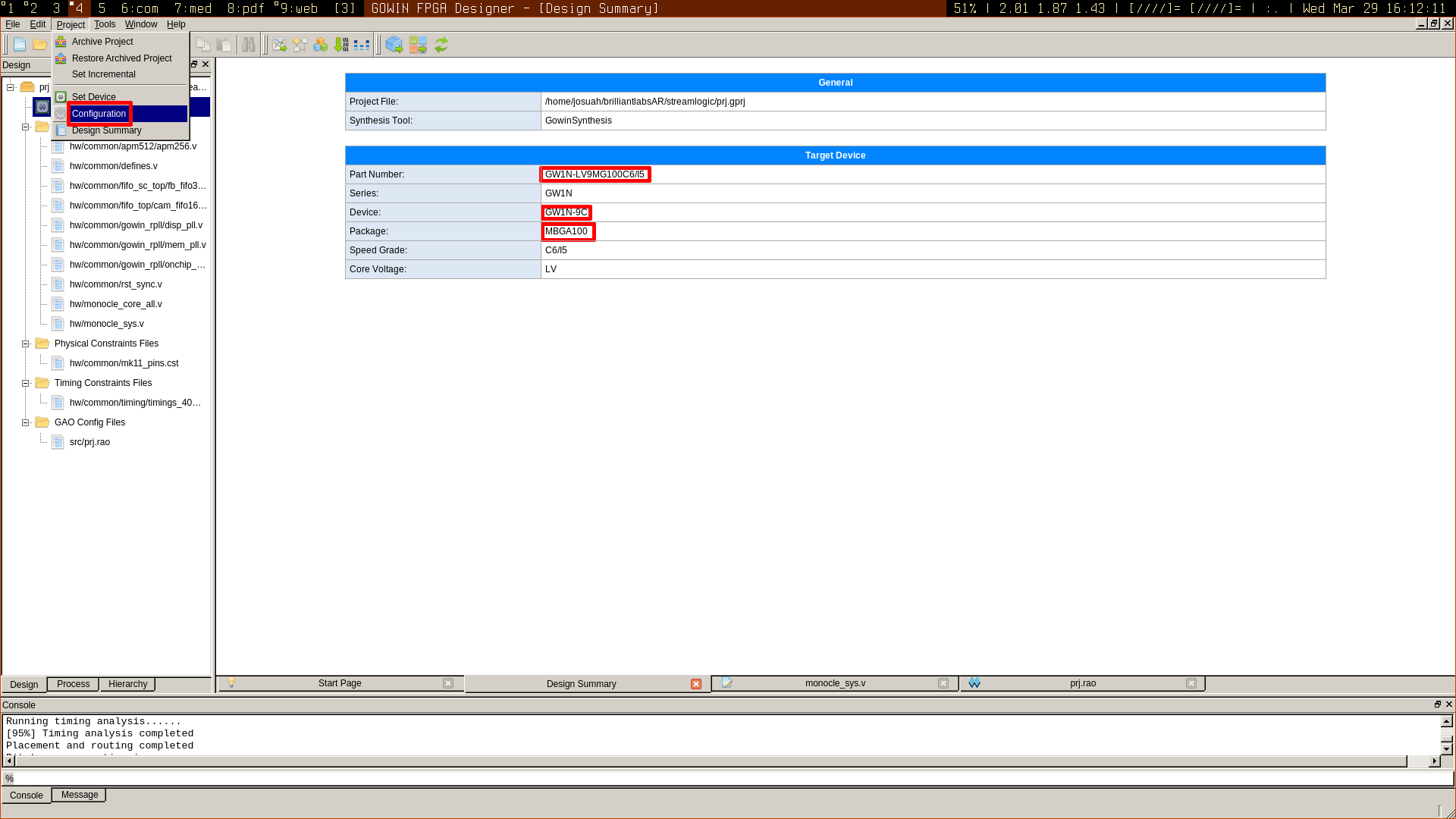

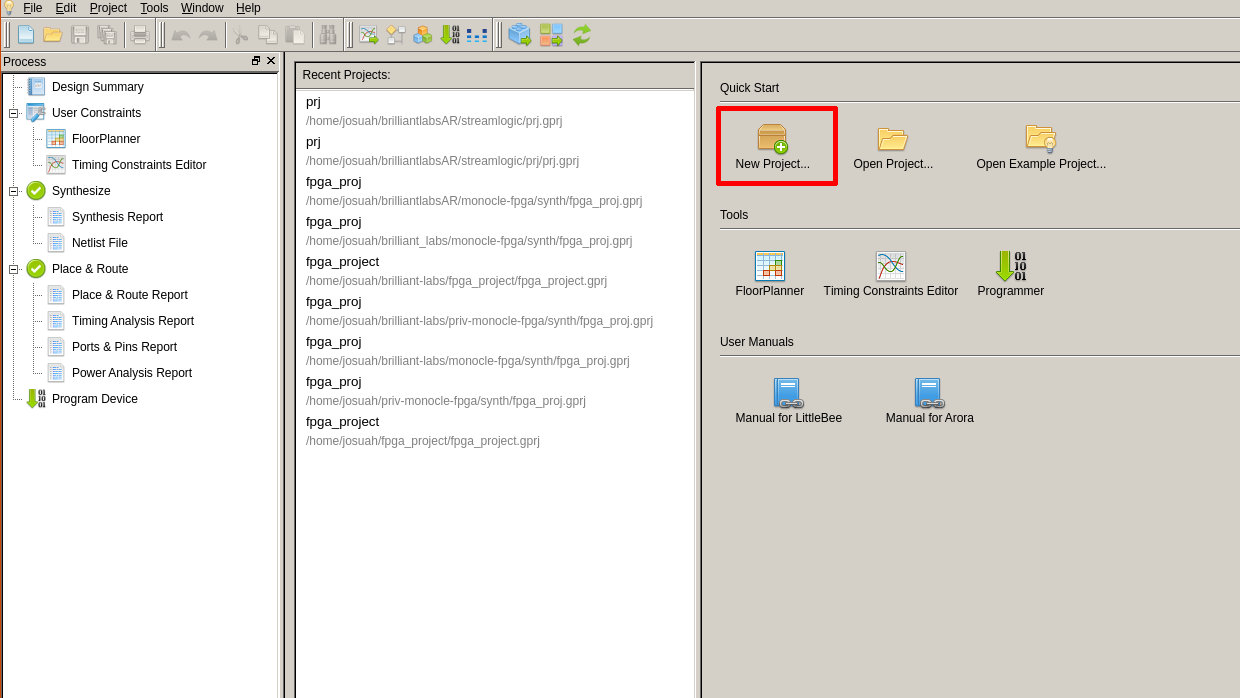

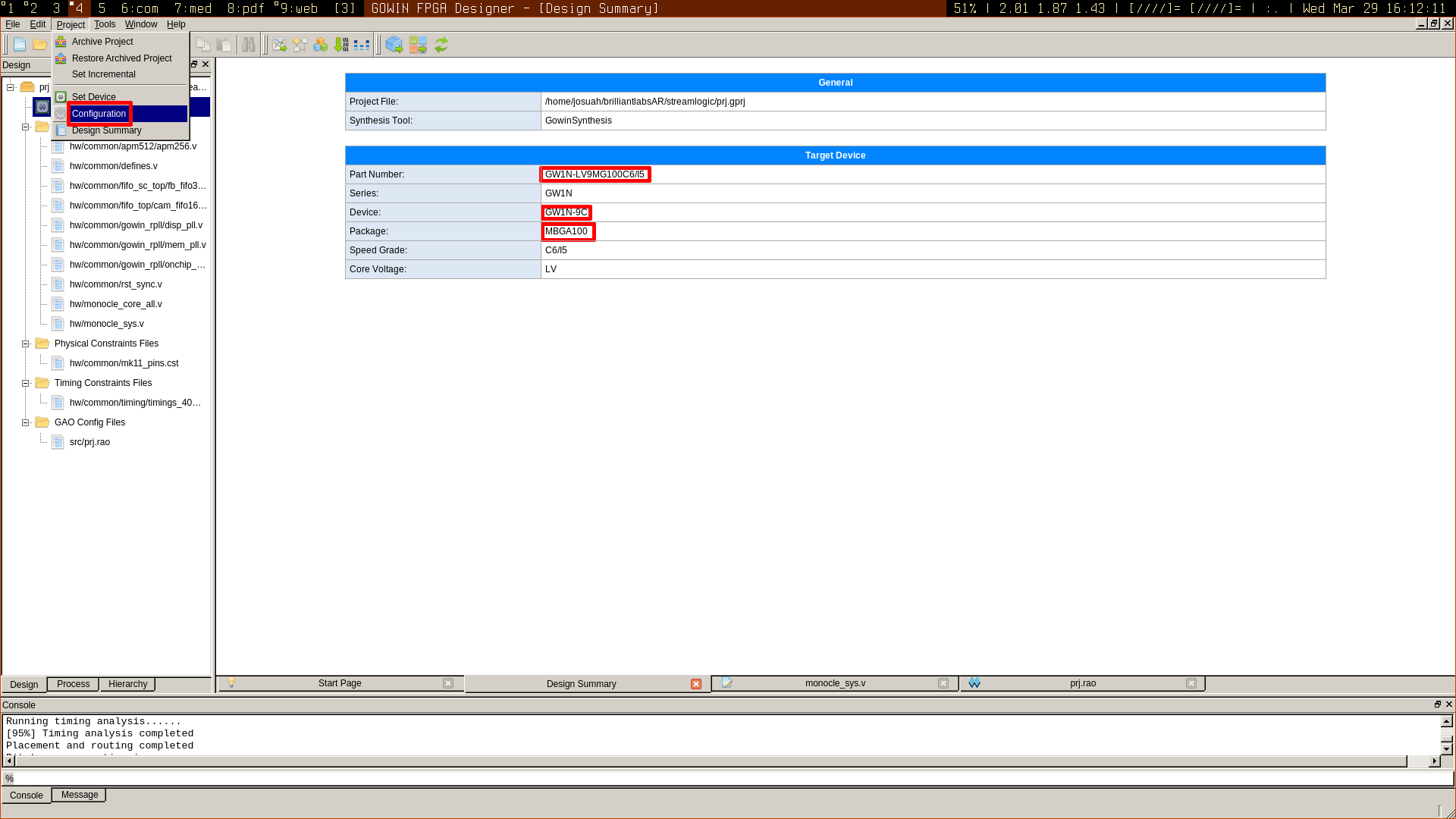

Step 01 - new project

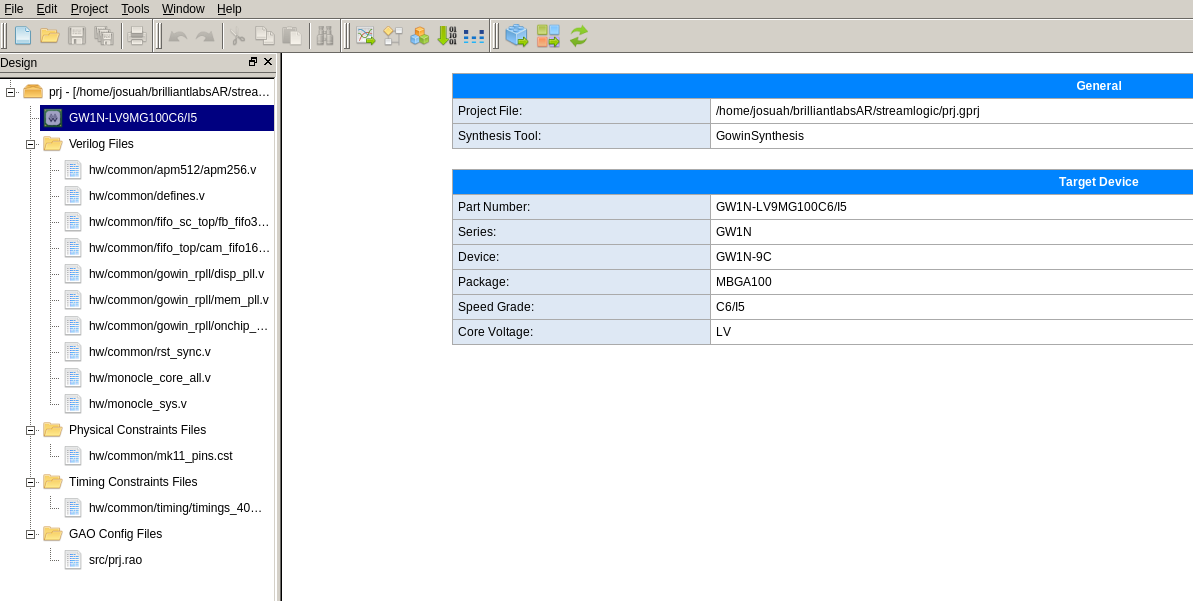

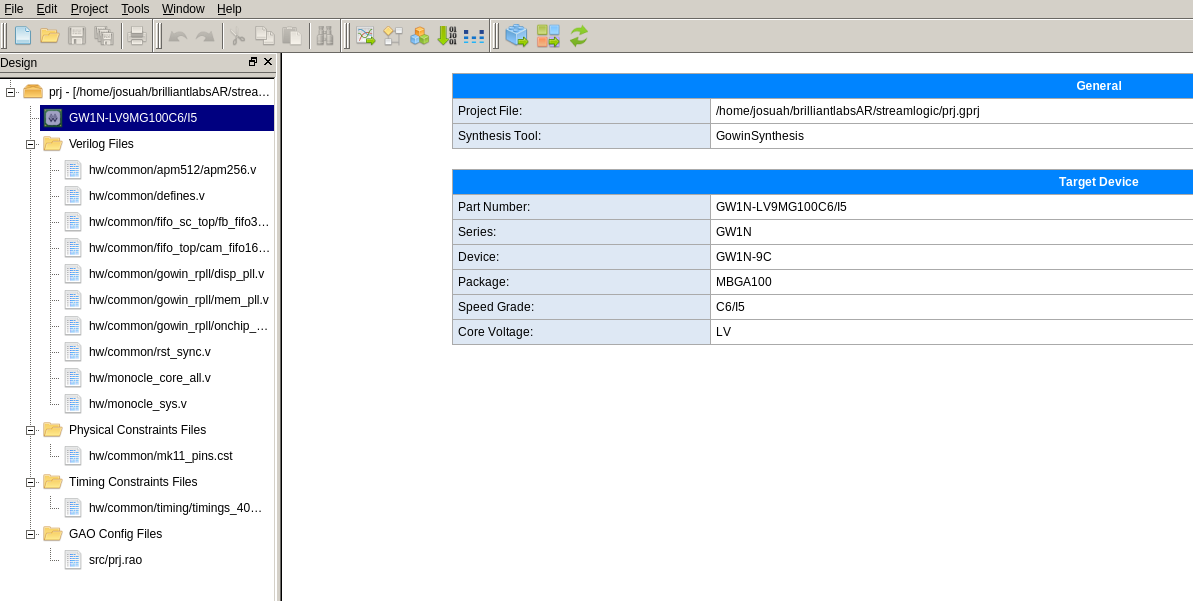

Step 02 - import all files from hw dir

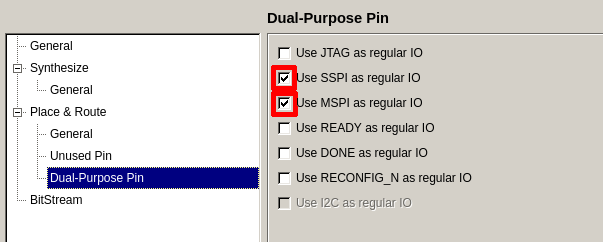

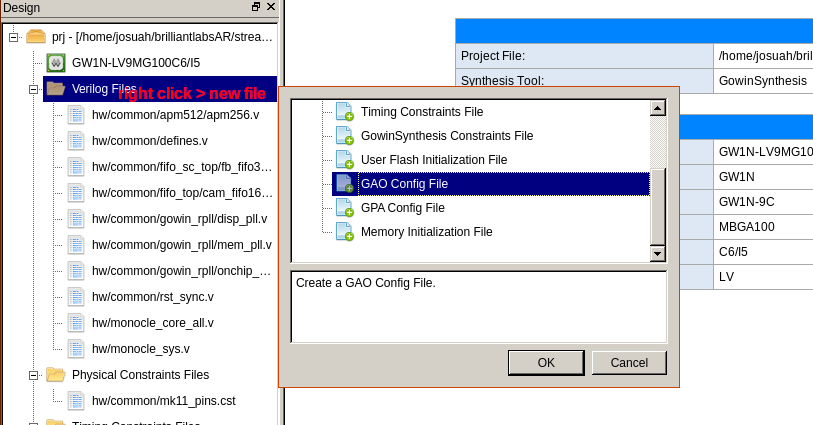

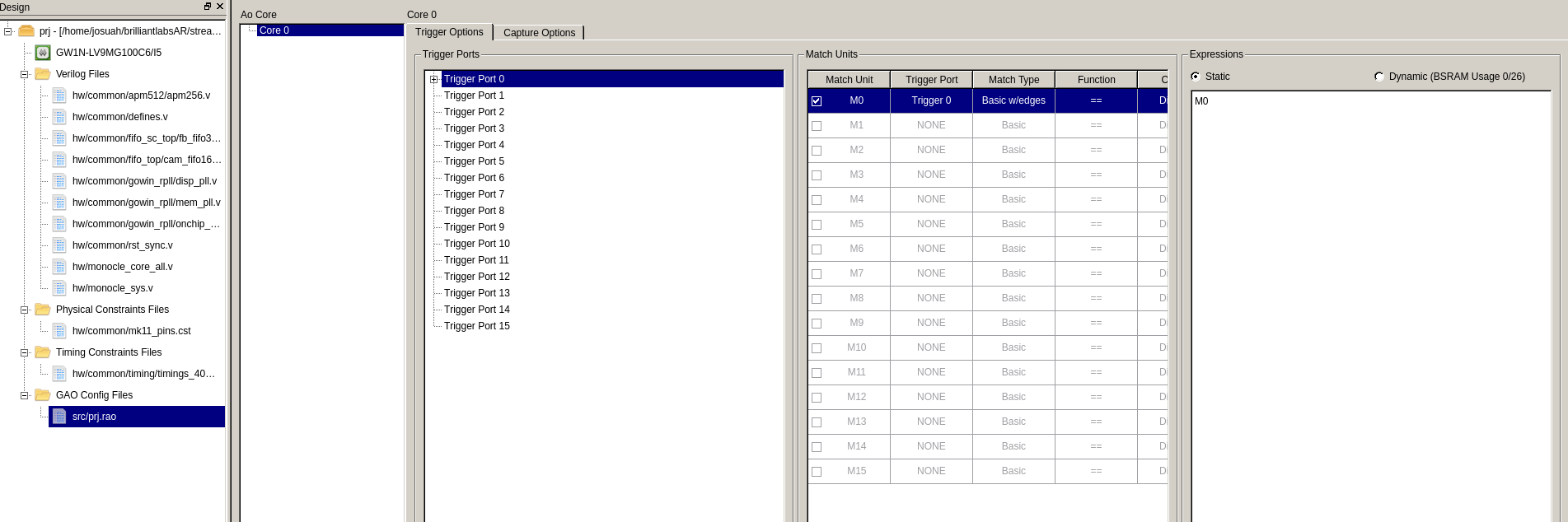

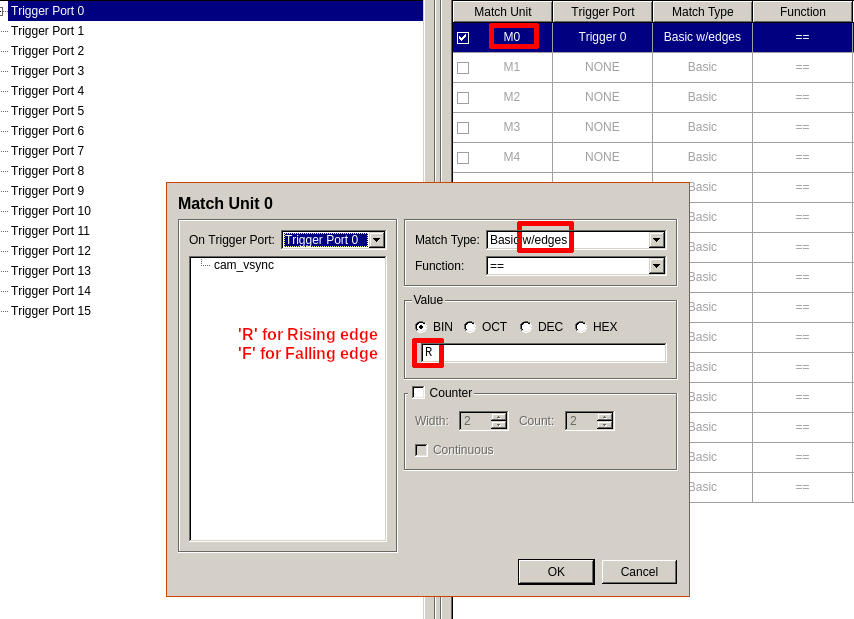

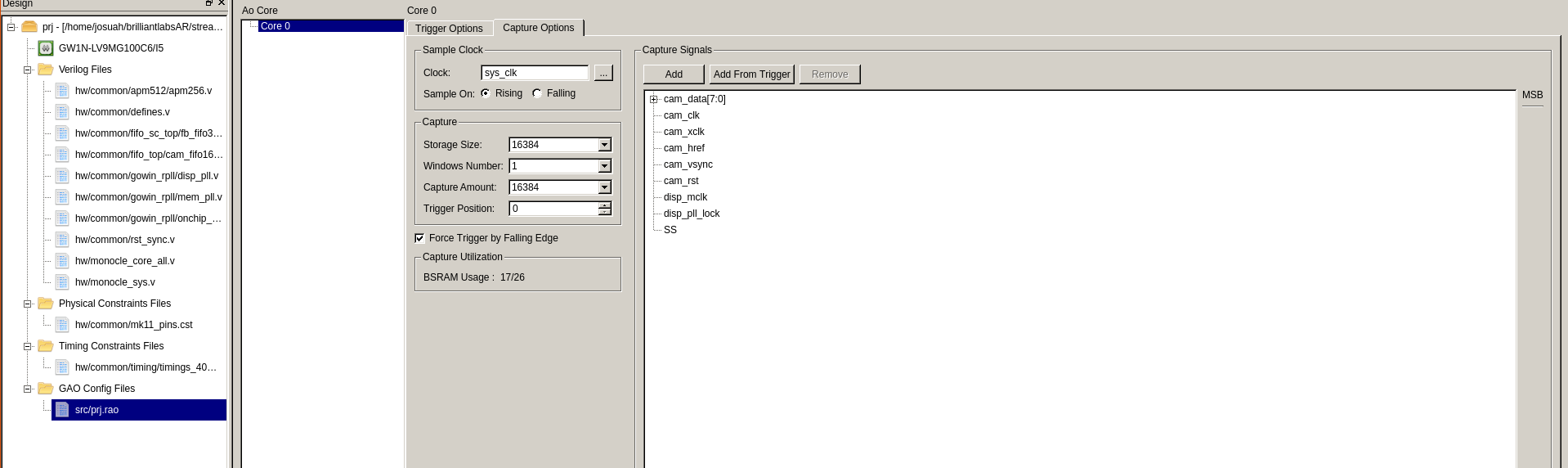

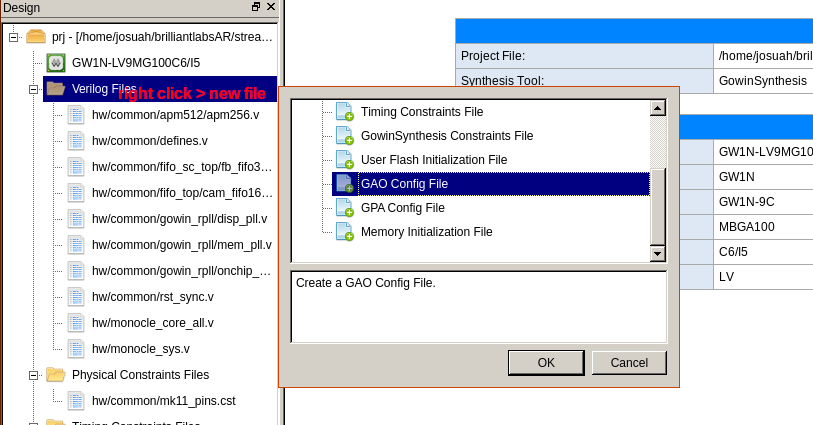

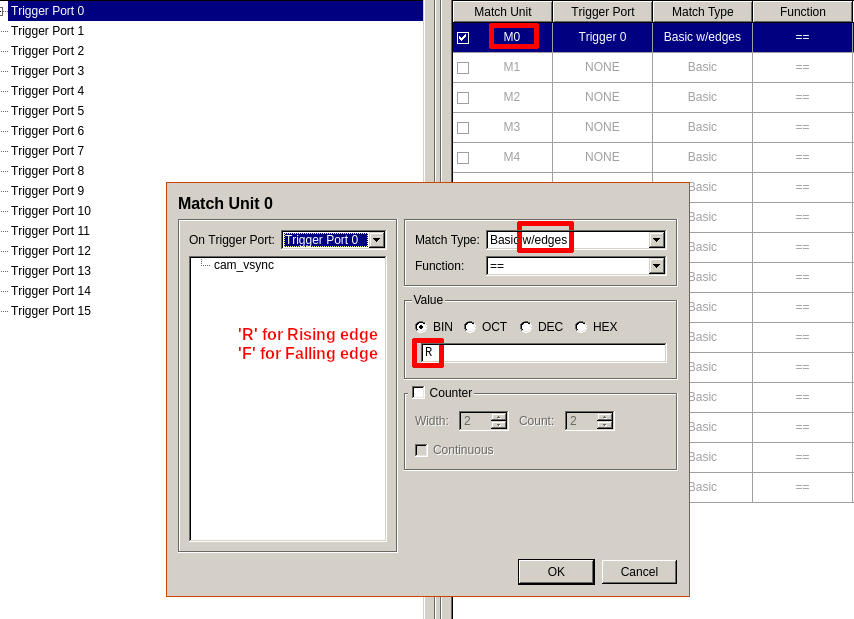

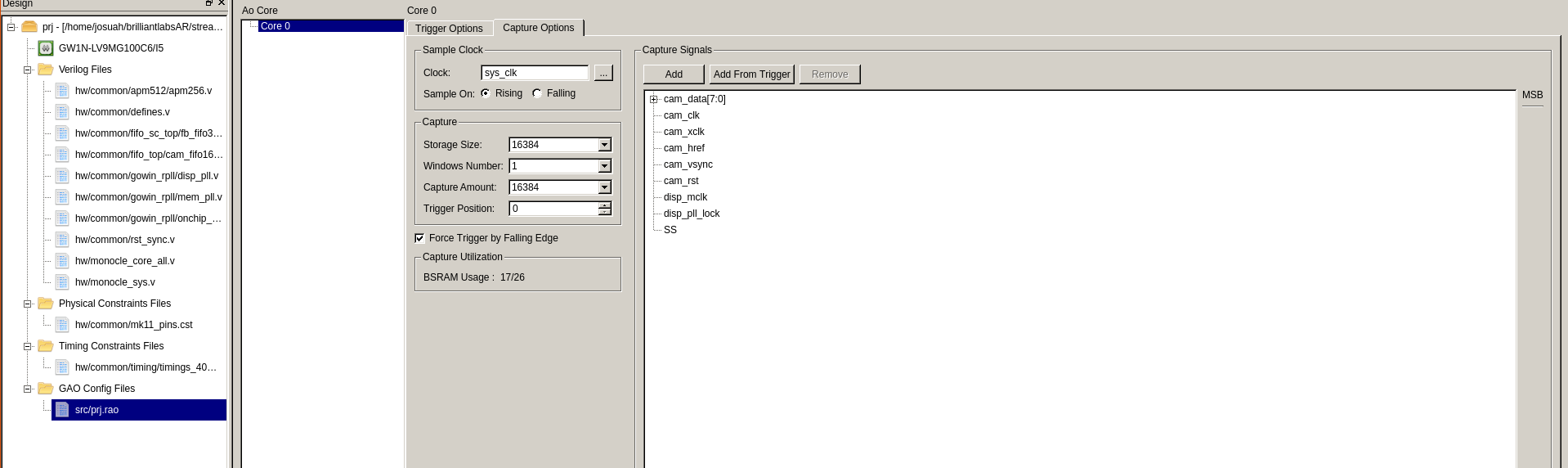

Step 05 - create new gao config

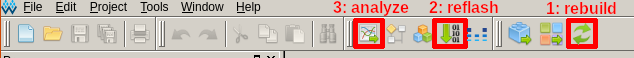

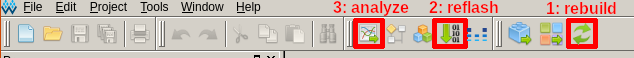

Step 09 - build the whole project program open gao

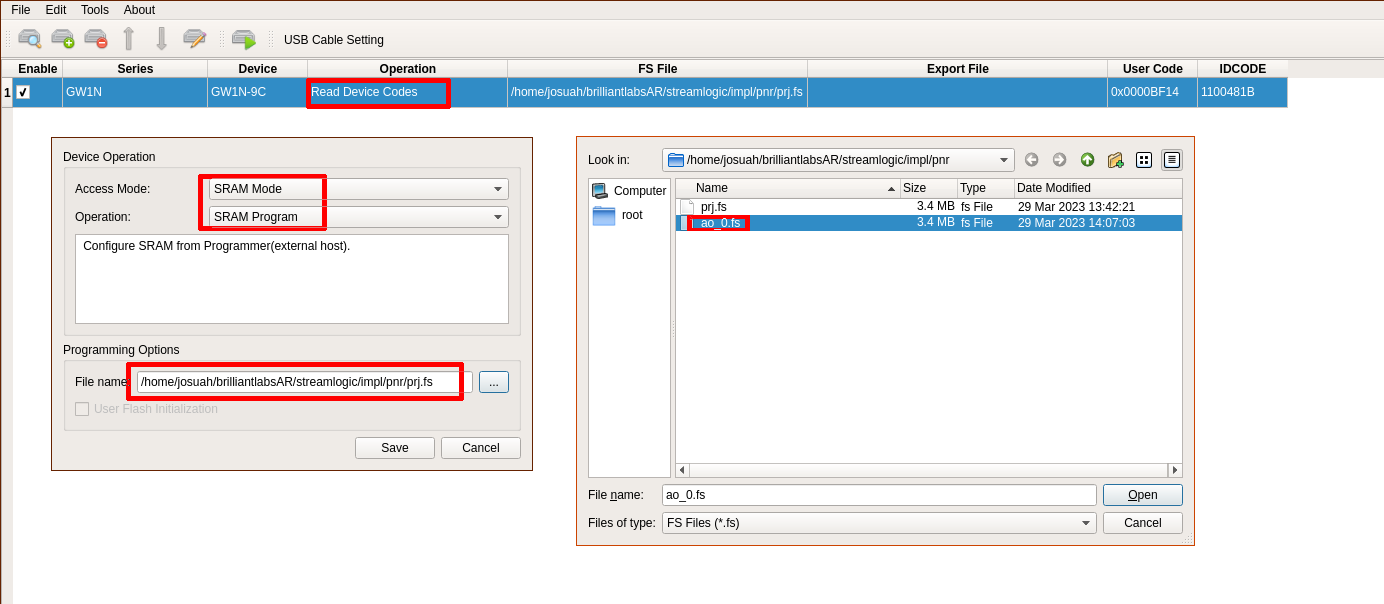

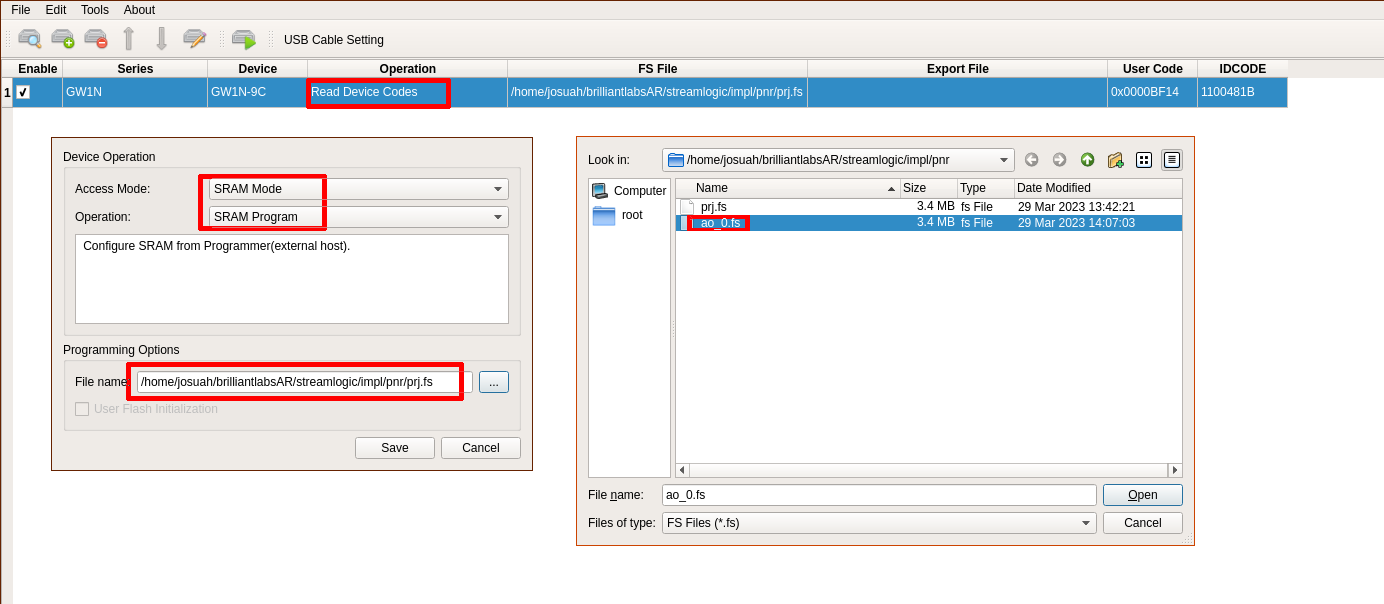

Step 10 - use sram or flash programming and choose ao 0 fs

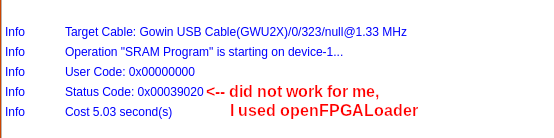

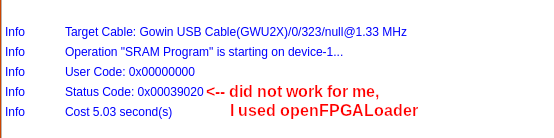

Step 11 - get the programming to work

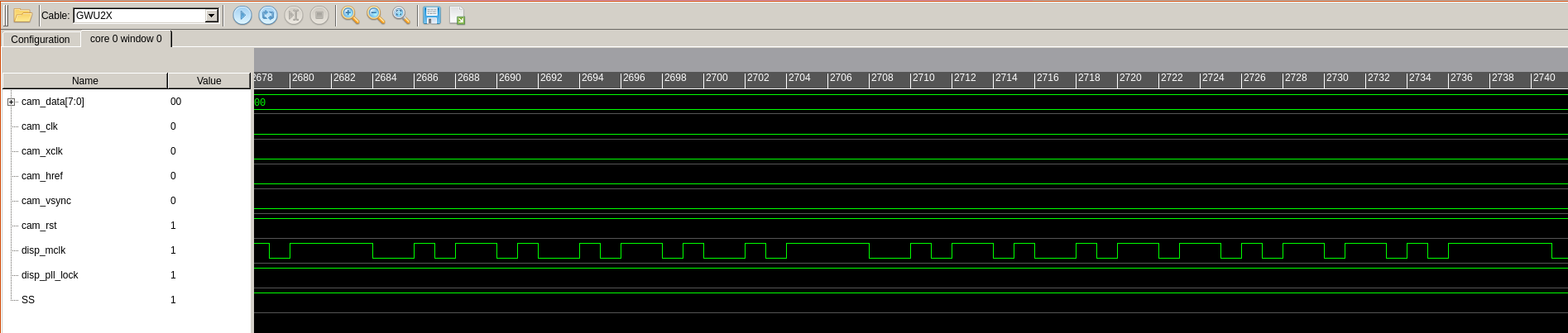

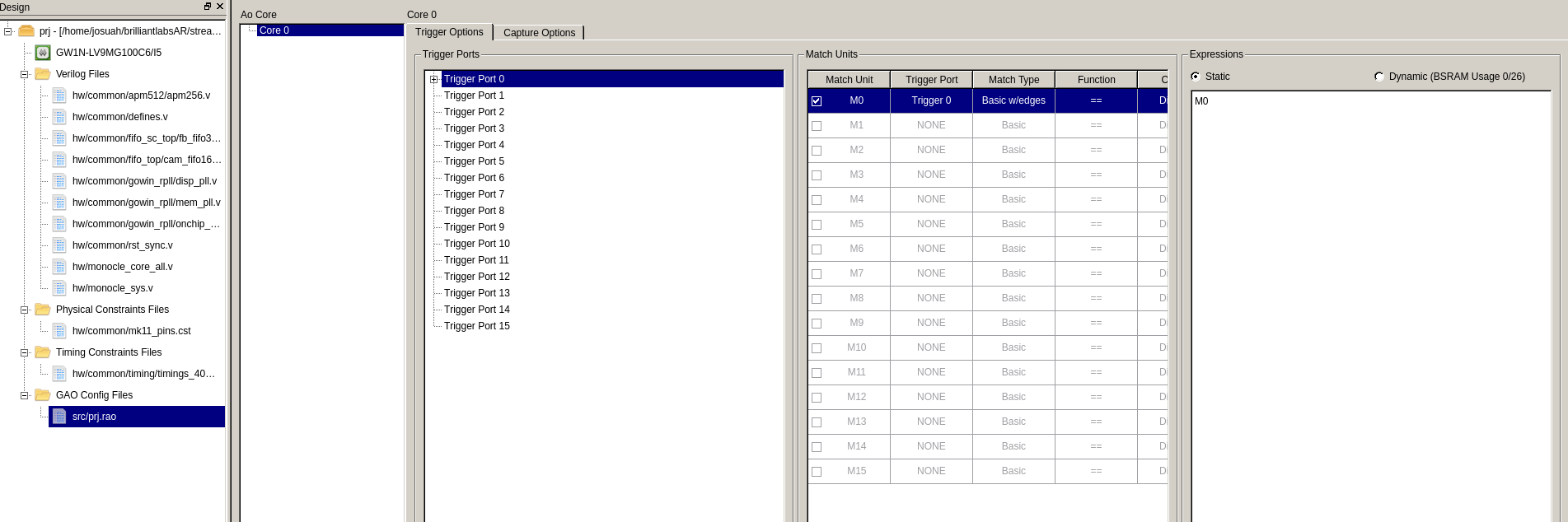

Step 12 - in gao select your dongle in the list and start the capture

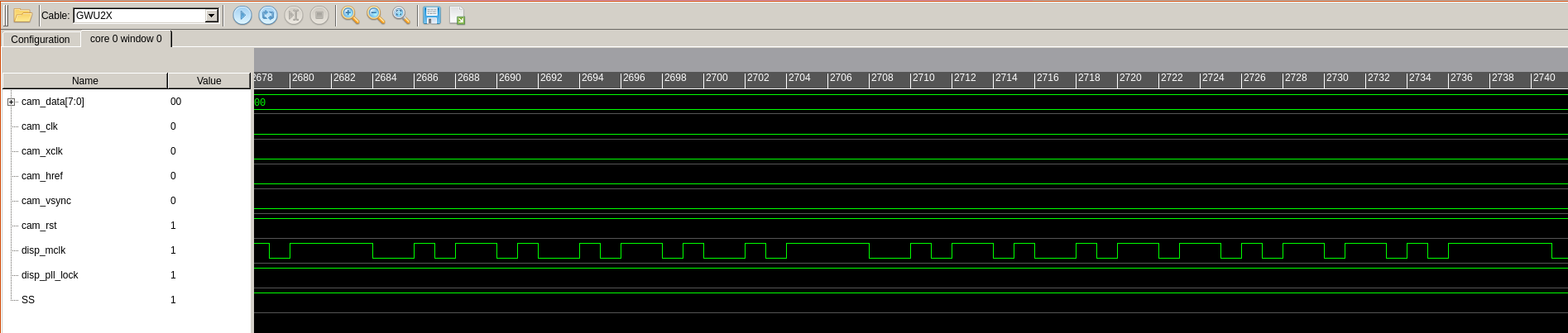

Step 13 - result if everything went fine